Programando a FPGA Tang Nano 9K

by Luan

Posted on 8 July 2023, 16:54

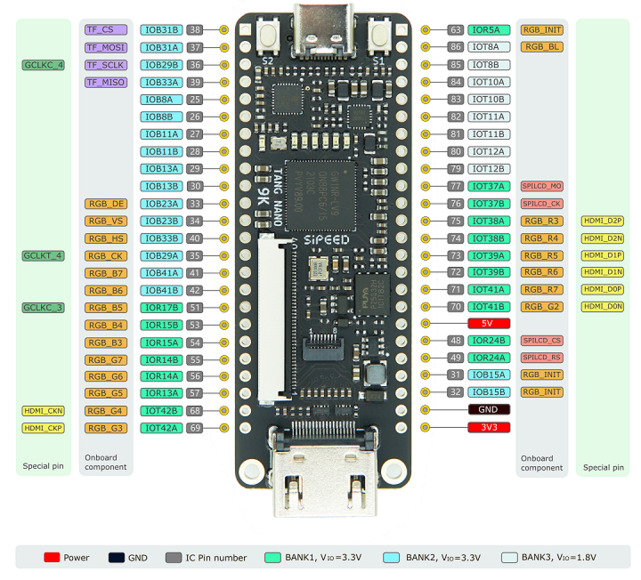

A FPGA Tang Nano 9K é uma placa de desenvolvimento compacta e poderosa, projetada para aplicações de baixo consumo de energia e alto desempenho.

- Obtendo e instalando a IDE

- Instalando o gravador

- Criando um projeto

- Criando o arquivo de descrição

- Síntese

- Configuração dos pinos e roteamento

- Gravando a FPGA

A FPGA Tang Nano 9K é uma placa de desenvolvimento compacta e poderosa, baseada na FPGA da Gowin. Projetada para aplicações de baixo consumo de energia e alto desempenho, a Tang Nano 9K oferece uma plataforma flexível para prototipagem, testes e implementação de sistemas digitais complexos. Com a tecnologia de matriz de portas programável em campo da Gowin, essa placa proporciona uma solução confiável e versátil para projetistas que desejam criar soluções personalizadas em uma variedade de domínios, como internet das coisas (IoT), processamento de sinais, automação industrial e muito mais. Com seu tamanho compacto e capacidade de processamento, a FPGA Tang Nano 9K é a escolha ideal para aplicações de alto desempenho em ambientes com restrições de espaço e energia.

Obtendo e instalando a IDE

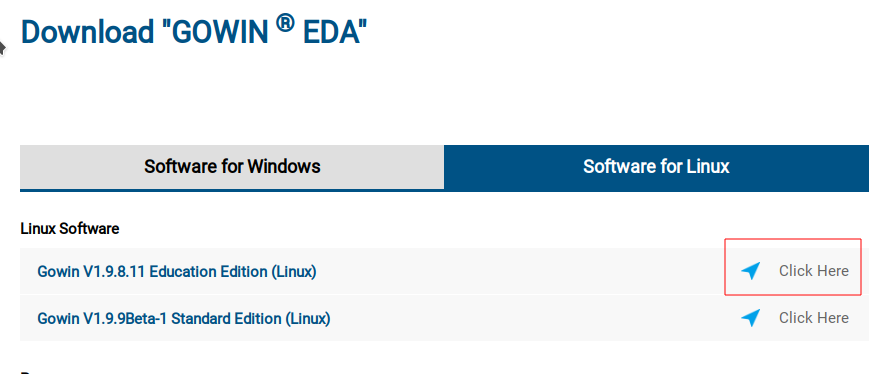

Para escrever a descrição do circuito em HDL e configuração do dispositivo, pinos etc. é preciso instalar a IDE. Ela pode ser obtida na seguinte URL: https://www.gowinsemi.com/en/support/download_eda/ .

Antes de fazer o Download é preciso fazer o registro.

No meu caso eu baixei a Education Edition para Linux.

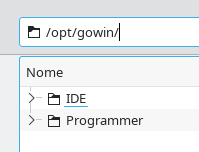

A instalação é feita de forma bem simples. Basta descompactar a o arquivo .tar.gz na pasta desejada. Descompactei na pasta /opt/gowin].

Para facilitar pode ser criado um icone na área de trabalho apontando para o executável da Ide da Gowin. Crie um arquivo de texto chamado gowin.desktop na área de trabalho com o seguinte conteúdo:

[Desktop Entry]

Categories=Development;IDE;Electronics;FPGA

Comment[pt_BR]=Gowin IDE

Comment=Gowin IDE

Exec=/opt/gowin/IDE/bin/gw_ide

GenericName[pt_BR]=Gowin IDE

GenericName=Gowin IDE

Icon=/opt/gowin/IDE/share/gowin

Keywords=embedded electronics;electronics;fpga

MimeType=

Name[pt_BR]=Gowin IDE

Name=Gowin IDE

Path=

StartupNotify=true

StartupWMClass=processing-app-Base

Terminal=false

TerminalOptions=

Type=Application

X-DBUS-ServiceName=

X-DBUS-StartupType=

X-KDE-SubstituteUID=false

X-KDE-Username=Lembre-se de tornar o arquivo gowin.desktop executável.

Instalando o gravador

O gravador que vem junto com a IDE não consegue detectar corretamente a placa Tang Nano. Para contornar isso é permitir a gravação pode ser utilizada outra ferramenta, o openFPGALoader.

As instruções para build e instalação do openFPGALoader são mostradas aqui: https://trabucayre.github.io/openFPGALoader/guide/install.html#linux

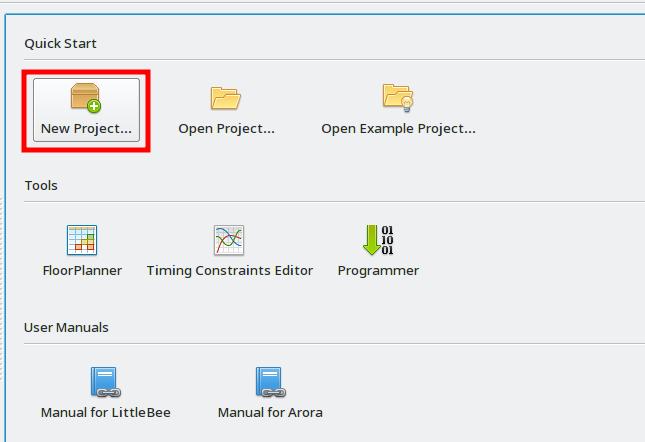

Criando um projeto

Para criar um projeto basta clicar no botão New Project na tela inicial da IDE:

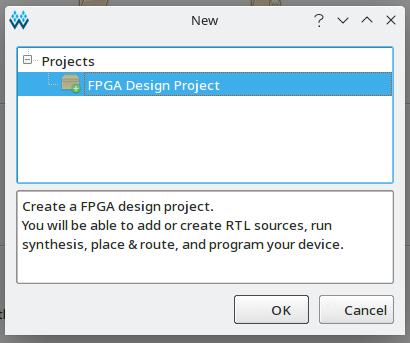

Depois escolher FPGA Design Project e clicar em OK:

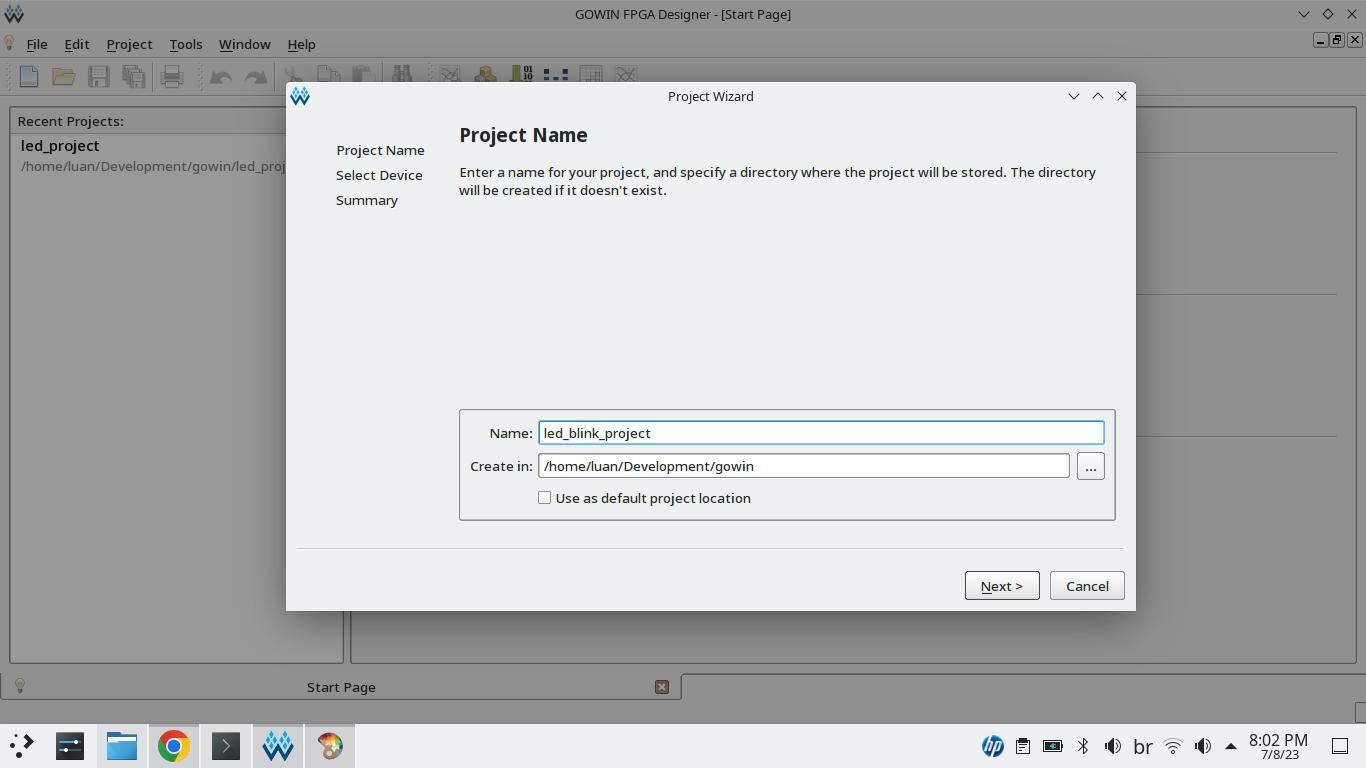

Preencher o nome do Projeto e o Diretório dos arquivos e clicar em Next:

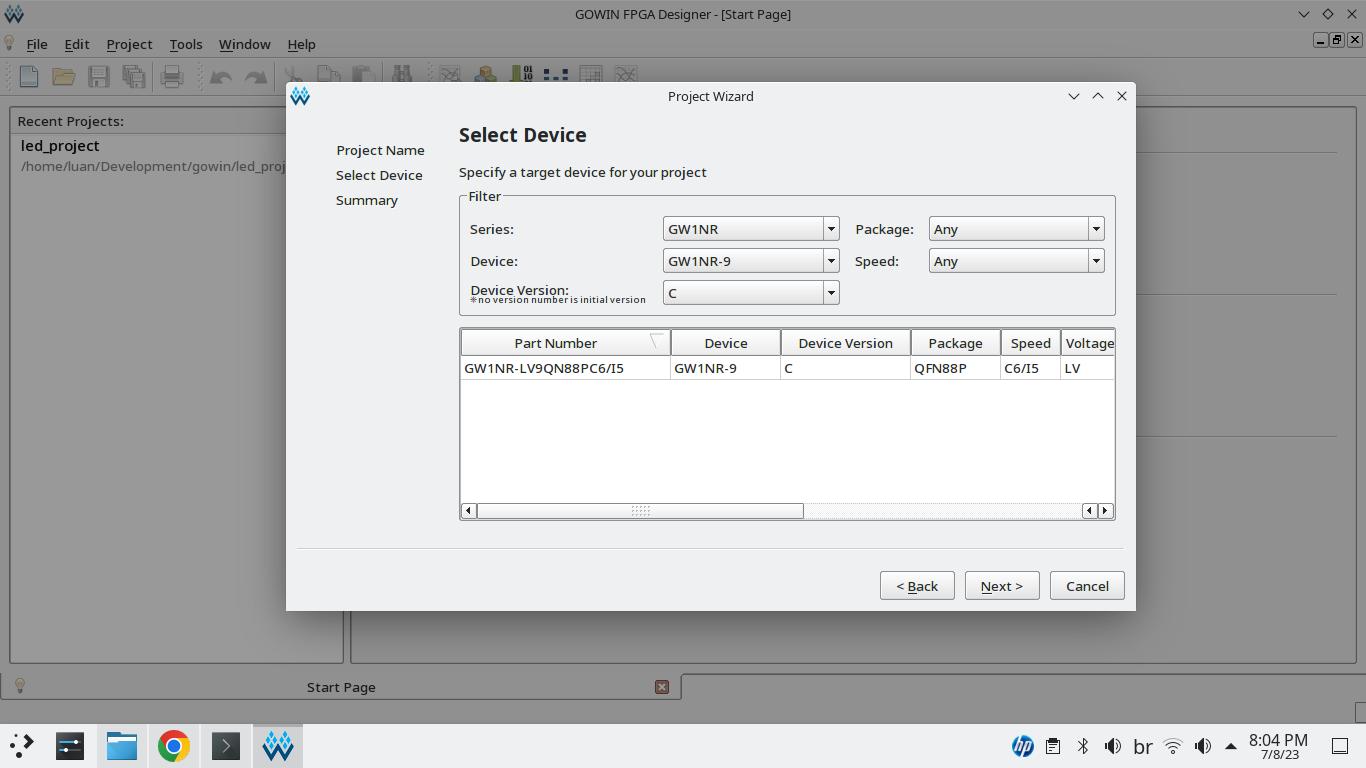

Selecione o dispositivo e clique em Next. Na Tang Nano 9K o dispositivo é GW1NR-9C QN88P:

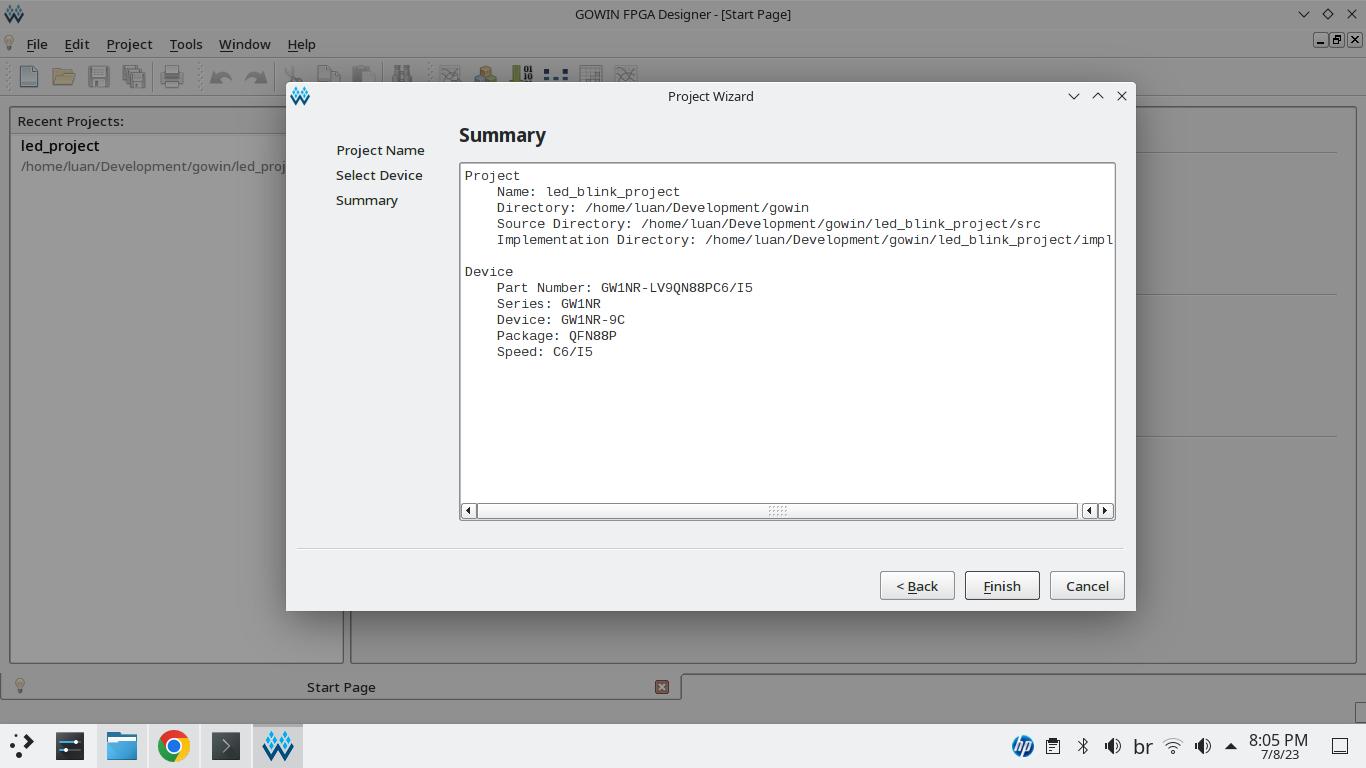

Confirme a configuração e clique em Finish:

Criando o arquivo de descrição

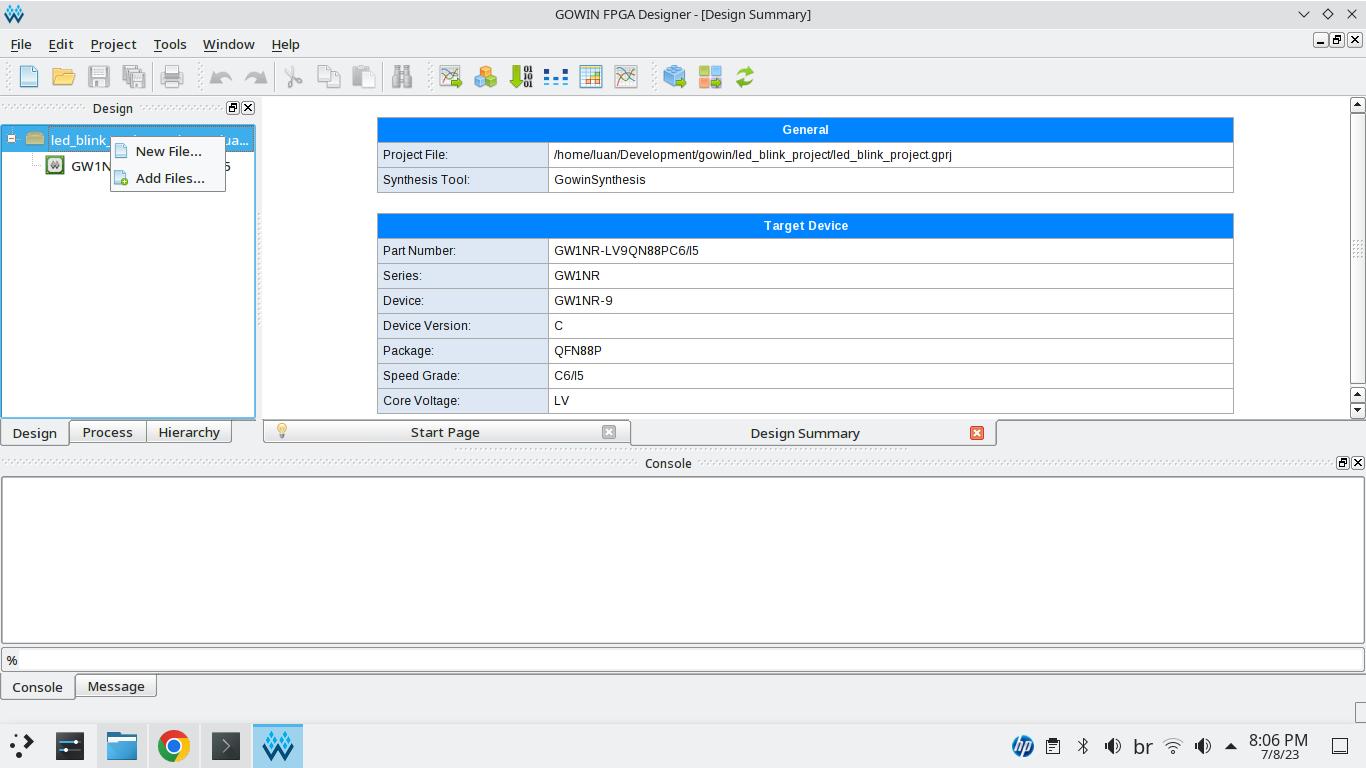

O próximo passo é a criação do arquivo com a descrição HDL. Neste exemplo utilizei VHDL. Para criar o arquivo, uma opção é clicar com o botão direito do mouse sobre o nome do projeto e clicar em New File…:

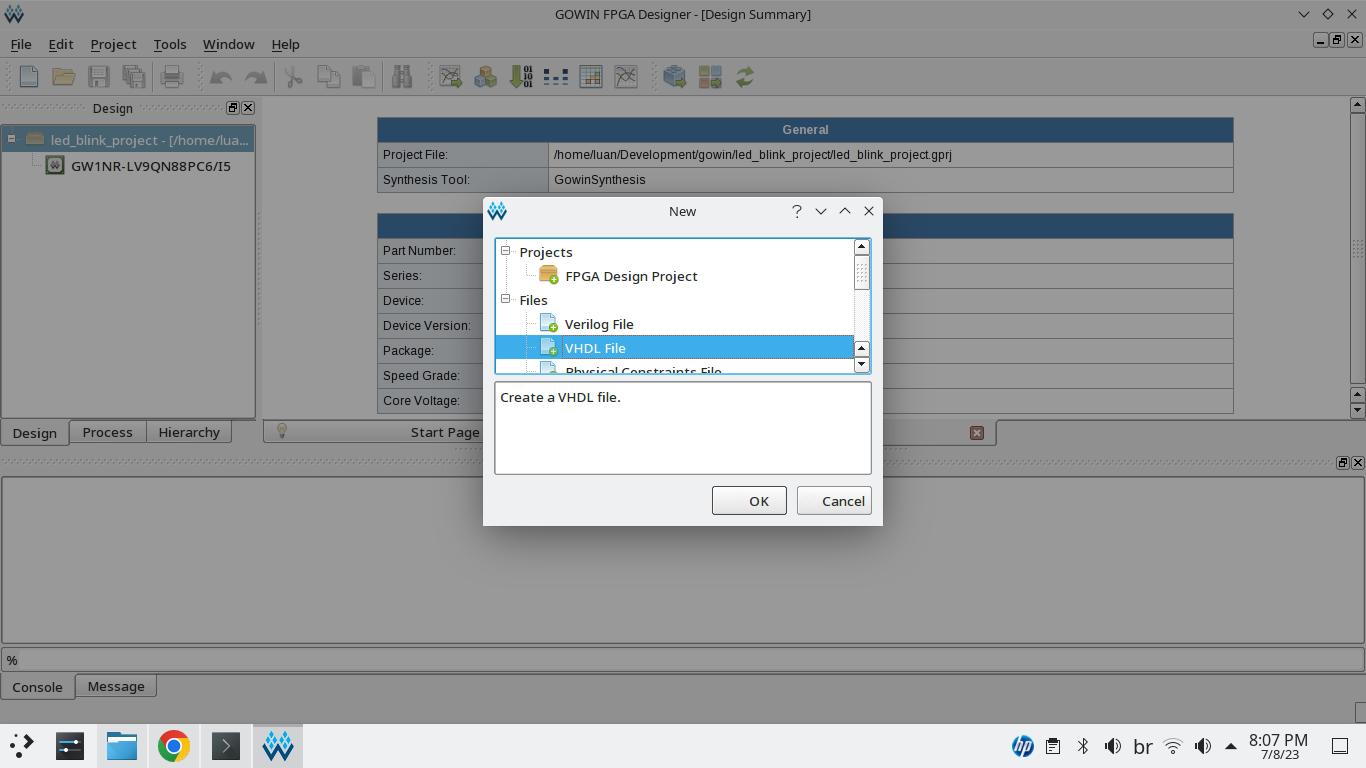

Depois basta escolher o tipo de arquivo VHDL File e clicar em OK:

O conteúdo do arquivo é mostrado a seguir:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use ieee.numeric_std.all;

entity blink is

port (

clk : in STD_LOGIC;

rst : in STD_LOGIC;

leds : out STD_LOGIC_VECTOR (5 downto 0)

);

end entity blink;

architecture a of blink is

signal leds_reg : STD_LOGIC_VECTOR (5 downto 0) := "111110";

signal cont: INTEGER range 1 to 9_000_000 := 1;

begin

process(clk, rst)

begin

if rst = '0' then

leds_reg <= "111110";

elsif rising_edge(clk) then

if cont = 9_000_000 then

cont <= 1;

leds_reg <= leds_reg(4 downto 0) & leds_reg(5);

else

cont <= cont + 1;

end if;

end if;

end process;

leds <= leds_reg;

end architecture a;O código mostrado utiliza os leds disponibilizados na própria Tang Nano 9K.

Síntese

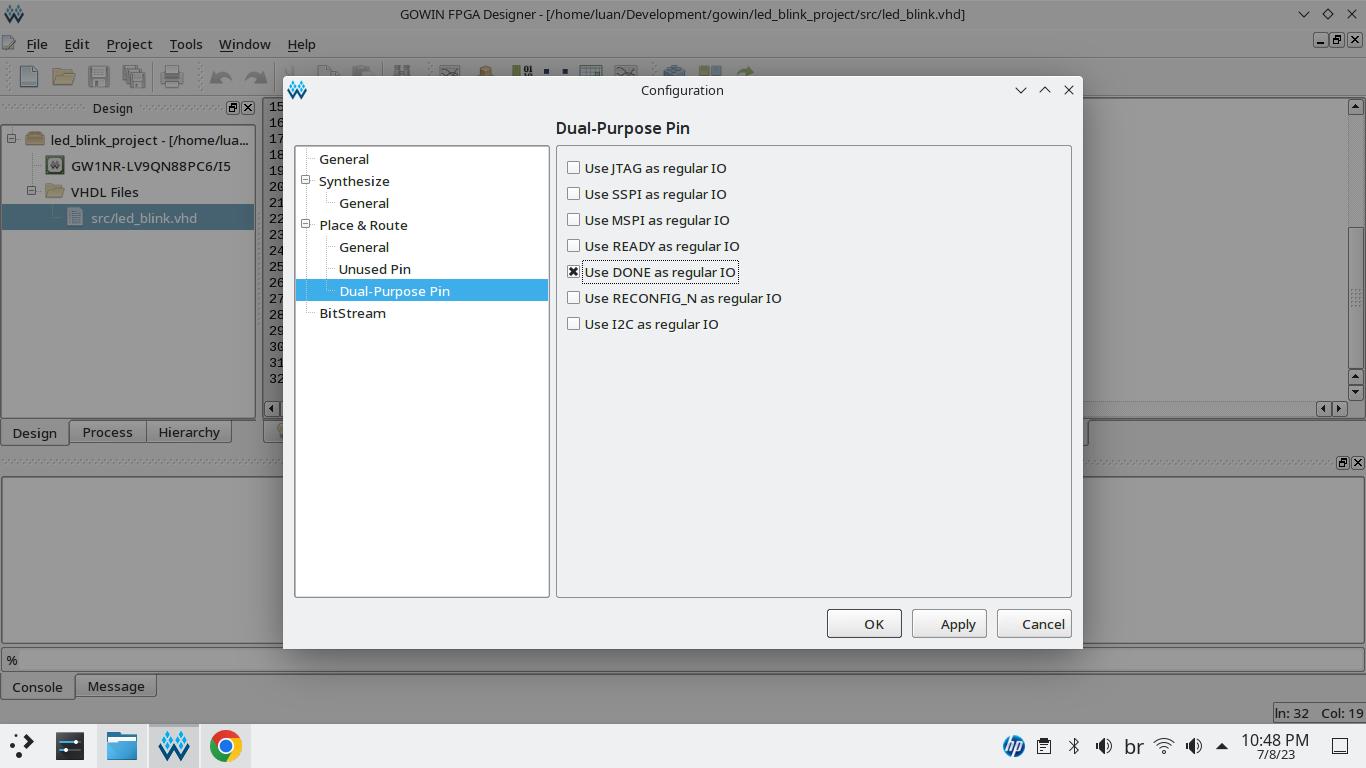

Clique no menu Project->Configuration e marque a opção Use DONE as regular IO em Place&Route->Dual-Purpose Pin e depois clique em Apply e OK:

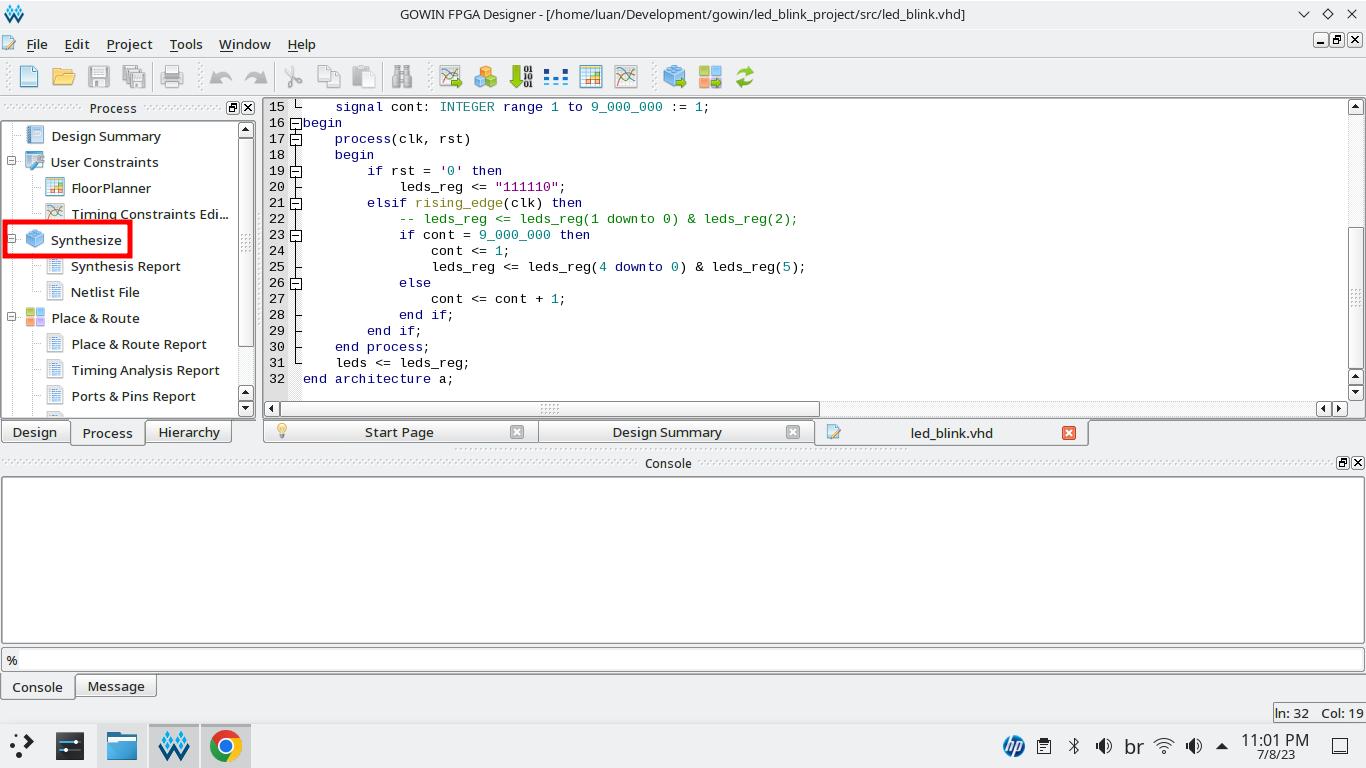

Para a realizar a Síntese do circuito clique na guia Process e dê um duplo clique em Synthesize:

Configuração dos pinos e roteamento

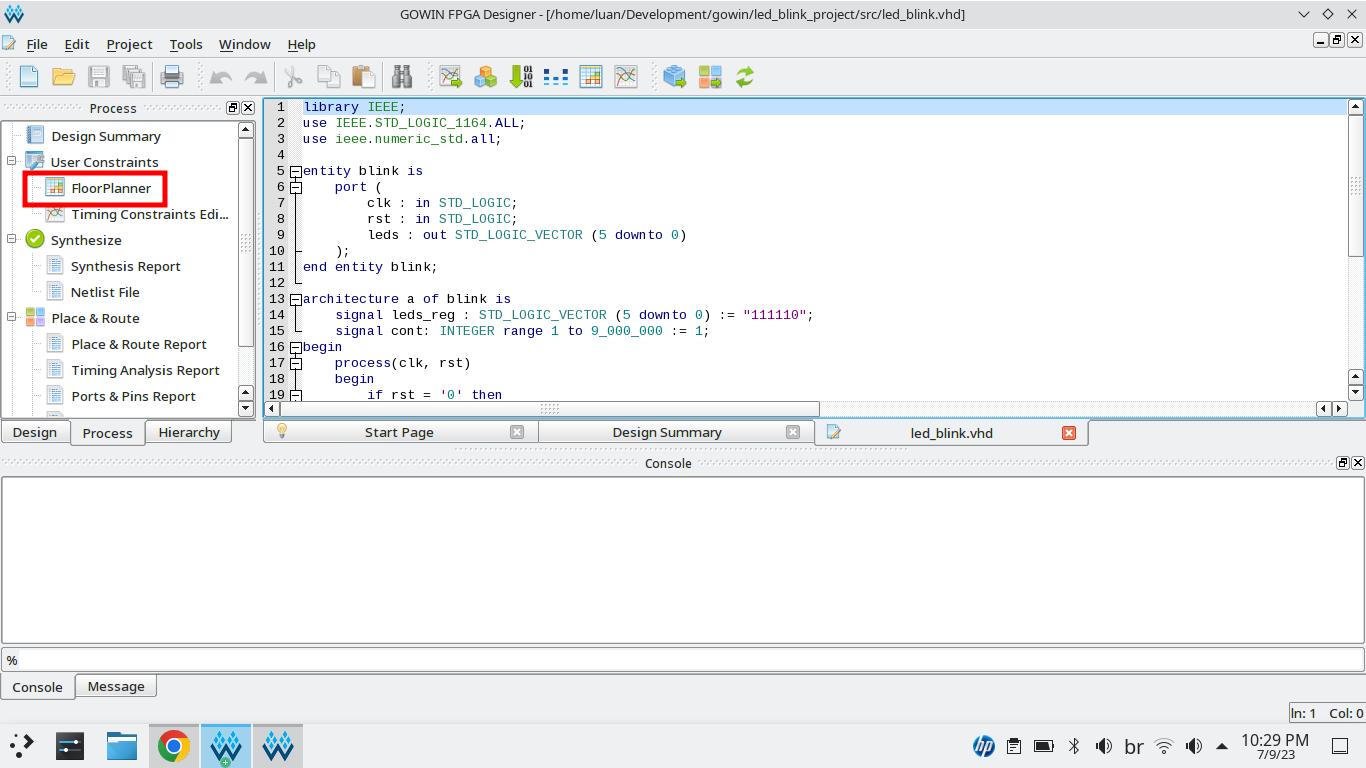

Após a síntese ser concluída com sucesso é preciso fazer o roteamento dos pinos do circuito gerado. Para definir as constraints do circuito dê um duplo clique em FloorPlanner.

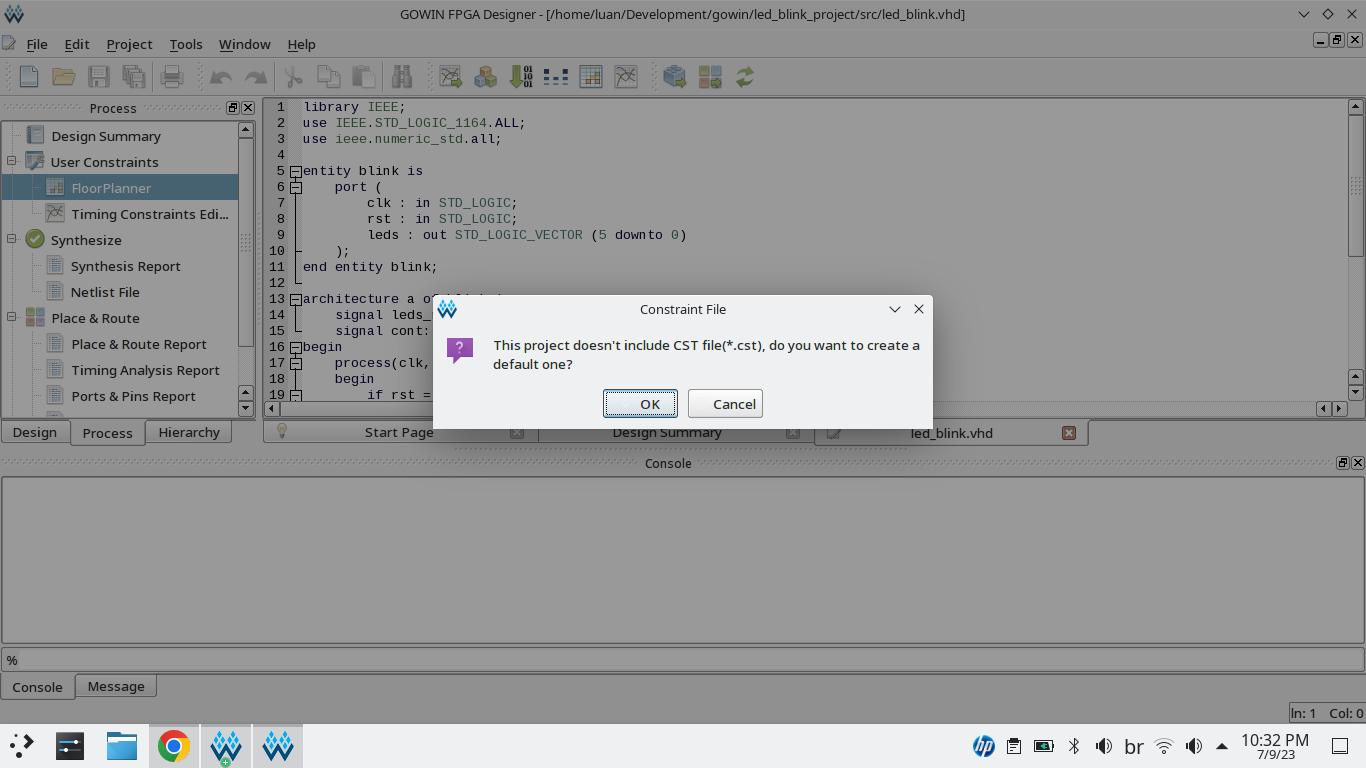

Na primeira execução será exibida uma tela sobre a criação do arquivo CST, basta clicar em OK.

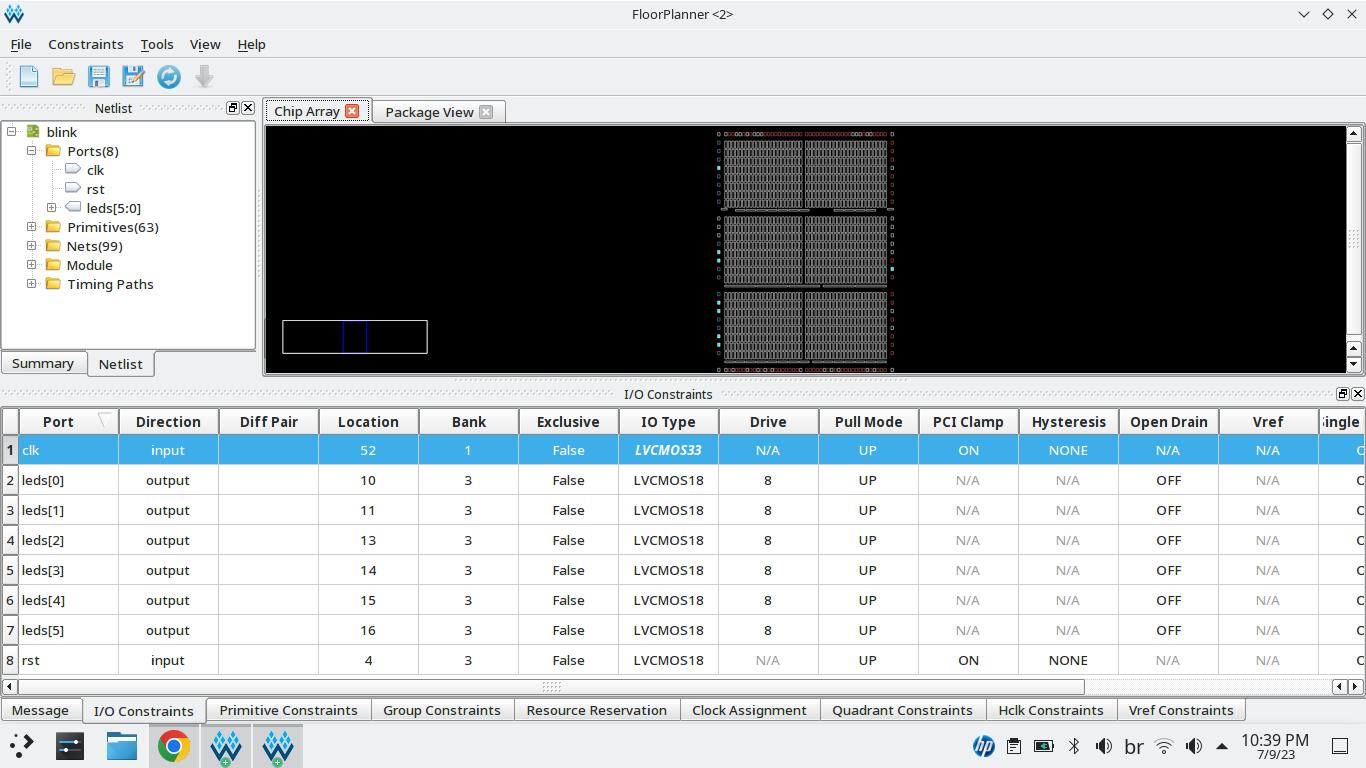

Defina as portas como mostrado a seguir e clique no botão Salvar:

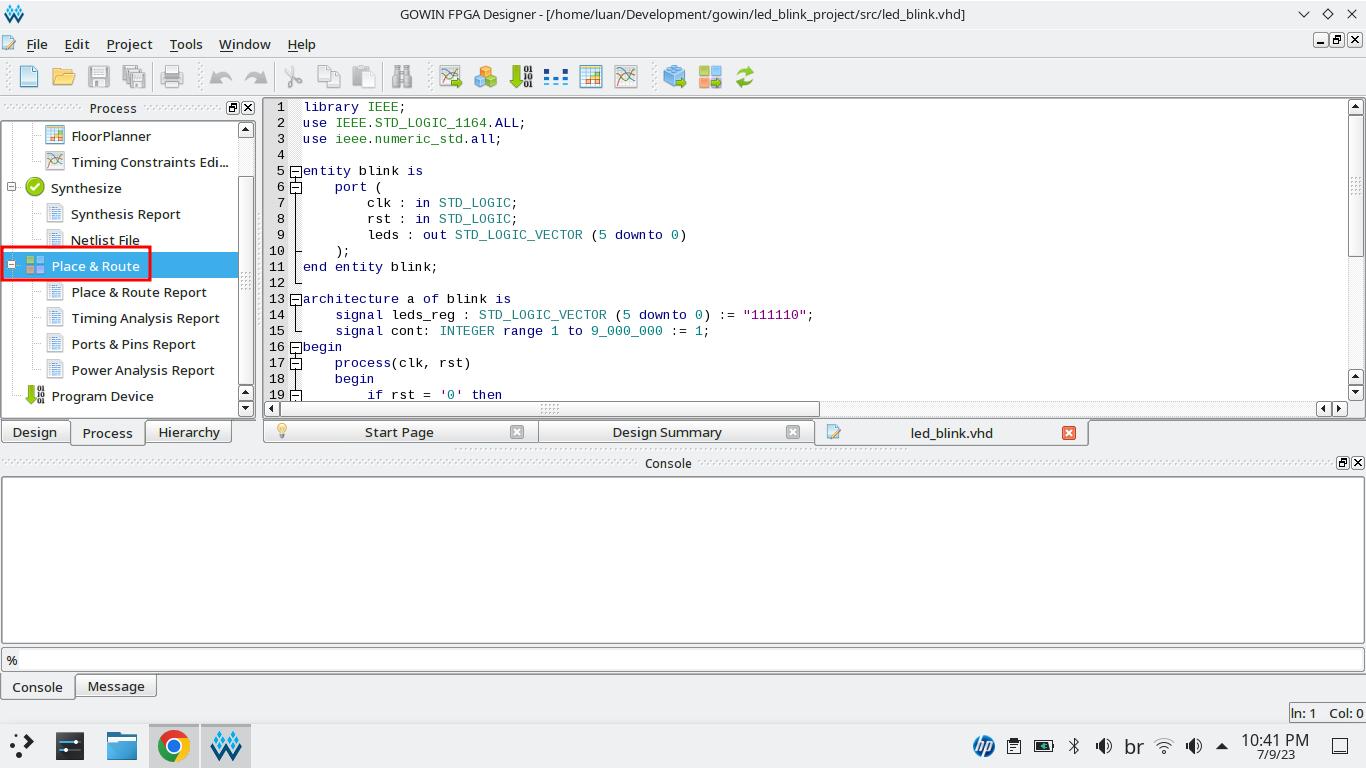

Após salvar a tela do FloorPlanner pode ser fechada. Na tela principal dê um duplo clique em Place & Route

Gravando a FPGA

Como dito anteriormente a ferramenta de gravação utilizada é a openFPGALoader. Para gravar basta usar o terminal.

openFPGALoader -b tangnano9k -f impl/pnr/led_blink_project.fsO comando acima faz a gravação na memória flash interna do dispositivo. A saída será como mostrada abaixo:

write to flash

Jtag frequency : requested 6.00MHz -> real 6.00MHz

Parse file Parse impl/pnr/led_blink_project.fs:

Done

DONE

Jtag frequency : requested 2.50MHz -> real 2.00MHz

erase SRAM Done

erase Flash Done

write Flash: [==================================================] 100.00%

DoneCom isso o processo de desenvolvimento e gravação do exemplo na FPGA está concluído.

Category Misc

Comments

Enter your comment below. Fields marked * are required. You must preview your comment before submitting it.

Search

About

I am computer engineer and MSc in Informatics graduated in Federal University of Espírito Santo. I am a programming and electronics enthusiast and I made this site to share my ideas and experiments in programming, electronics and DIY. I hope you enjoy it.

Donate: monero

452LPJcRqkhiaMdwpJSrzY1CTQ6MQMDxxQkUwDHDjBCe3Pcb6p9dHnGBZYjhZX1gHGU86W8wunHJBVDx5bk2K2aoFYwSA36